Transistor-Transistor logic

Transistor-Transistor Logic ou TTL est une famille de circuits logiques utilisée en électronique, inventée en 1961[1] par James L. Buie (en) sous l'appellation Transistor-Coupled Transistor Logic. De façon indépendante, inspirée par une présentation[2] de la société Fairchild sur les techniques de logique tout-transistor, la société Sylvania a produit les premiers circuits intégrés TTL commerciaux en 1963. Développée et proposée par de nombreux fabricants électroniques, la famille TTL a rapidement constitué une norme de premier plan pour les circuits intégrés utilisés dans les ordinateurs et les appareils numériques.

Cette famille emploie une technologie à transistor bipolaire saturé – par opposition aux technologies à transistor bipolaire non saturé (p. ex. famille ECL) et à transistor à effet de champ (p. ex. familles NMOS, PMOS, CMOS, HCMOS) – distincte des technologies à résistance et transistor (p. ex. famille RTL). Elle constitue une amélioration de la famille des portes logiques DTL (Diode-Transistor Logic) apparue dans la seconde moitié des années 1950. Aujourd'hui elle tend à disparaître du fait de sa consommation énergétique élevée (comparativement aux circuits CMOS).

Principe de fonctionnement[modifier | modifier le code]

Dans sa version primitive[1],[2], la structure d'une porte TTL élémentaire (en l'occurrence une porte inverseuse – opérateur NON) est constituée de deux transistors bipolaires de même type (communément de type NPN) et d'une résistance, soit :

- un transistor de couplage, monté en base commune, dont l'émetteur est relié à l'entrée de la porte ;

- un transistor d'amplification et d'inversion, monté en émetteur commun, dont la base est reliée au collecteur du transistor de couplage, l'émetteur à la masse et le collecteur à la sortie de la porte ;

- une résistance, connectée entre la base du transistor de couplage et l'alimentation (au pôle positif dans le cas de transistors NPN), qui fournit le courant nécessaire au fonctionnement de la porte.

Les deux transistors fonctionnent en mode de commutation : chaque transistor est soit saturé (VCE faible) et équivalent à un interrupteur fermé entre son collecteur et son émetteur, soit bloqué (IC négligeable) et équivalent à un interrupteur ouvert entre son collecteur et son émetteur.

Lorsqu'un niveau de tension bas est appliqué à l'entrée de la porte en drainant vers la masse le courant qui en sort (situation représentative d'un état logique 0) :

- le transistor de couplage est saturé par le courant issu de la résistance qui traverse sa jonction base-émetteur

- le transistor d'amplification et d'inversion est bloqué car sa tension base-émetteur est insuffisante

- le circuit extérieur relié à la sortie de la porte peut produire un niveau de tension haut (représentatif d'un état logique 1).

Lorsque le courant produit par l'entrée de la porte n'est pas drainé vers la masse ou lorsqu'on applique un niveau de tension élevé sur cette entrée (situation représentative d'un état logique 1) :

- le transistor de couplage est bloqué† car sa tension base-émetteur est insuffisante ou négative‡

- le transistor d'amplification et d'inversion est saturé par le courant issu de la résistance qui traverse la jonction base-collecteur du transistor de couplage

- le transistor d'amplification et d'inversion impose à la sortie de la porte un niveau de tension bas (représentatif d'un état logique 0) en drainant vers la masse le courant issu du circuit extérieur.

Remarques :

† : le blocage du transistor de couplage correspond à IE nul avec une inversion du rôle de son émetteur (E) et de son collecteur (C) du fait de sa polarisation particulière. Ce blocage survient sans dé-saturation notable du transistor[1], ce qui procure des temps de commutation très courts.

‡ : afin d'assurer le blocage du transistor de couplage lors de l'inversion du rôle de son émetteur et de son collecteur par l'application d'une tension élevée (p. ex. 5 V) sur l'entrée de la porte, celui-ci est fabriqué de sorte que son gain en courant inverse reste très faible.

Pour réaliser un opérateur logique NON-ET, on utilise un transistor de couplage multi-émetteurs dont chaque émetteur est relié à une entrée du circuit, de sorte que ce transistor n'est bloqué, et produit donc un niveau bas sur la sortie de la porte (état logique 0), que lorsque toutes les entrées sont au niveau haut (état logique 1).

Ainsi, les jonctions base-émetteur du transistor de couplage réalisent une opération logique ET à la manière d'un circuit logique à diodes (p. ex. DTL), puis le transistor d'amplification et d'inversion réalise une opération logique NON.

Par exemple, pour trois entrées logiques A, B et C produisant l'état de la sortie logique Y, le transistor de couplage réalise d'abord l'opération X = A.B.C, puis le transistor d'amplification et d'inversion réalise l'opération Y = ¬X = ¬(A.B.C) .

Pour réaliser un opérateur logique NON-OU, on utilise des portes NON dont les collecteurs des transistors d'amplification et d'inversion sont interconnectés, de sorte que la tension de sortie est forcée au niveau bas (état logique 0) dès que la tension d'au moins l'une des entrées est au niveau haut (état logique 1).

Ainsi, les transistors d'amplification et d'inversion réalisent chacun une opération logique NON puis, ensemble, une opération logique ET à la manière d'un circuit à couplage direct (p. ex. DCTL).

Par exemple, pour trois entrées logiques A, B et C produisant l'état de la sortie logique Y, les portes NON réalisent d'abord les opérations U = ¬A, V = ¬B et W = ¬C, puis l'interconnexion des transistors d'amplification et d'inversion réalise l'opération Y = U.V.W = ¬A.¬B.¬C = ¬(A+B+C) .

On réalise une opération logique ET-OU-NON en combinant directement les deux montages NON-ET et NON-OU précédents.

En pratique, dans les différentes séries de circuits TTL qu'ils proposent, dès le départ les constructeurs mettent en œuvre cette structure primitive en y apportant des améliorations visant notamment à augmenter ses performances (vitesse, consommation, immunité au bruit, fan-out, fan-in, etc.).

En particulier, le transistor d'amplification et d'inversion n'est plus connecté directement à la sortie du circuit logique, mais il pilote un étage amplificateur push-pull (totem-pole), ou à trois-états, ou à collecteur ouvert.

La présence systématique de cet étage de sortie a conduit à normaliser les seuils de tension des niveaux logiques TTL à des valeurs supérieures à celles de la structure primitive de Buie (0,8 V et 2 V[4] au lieu de 0,2 V et 0,8 V environ[1] pour les niveaux bas et haut respectivement).

Les séries de circuits TTL les plus récentes (LS, F, AS, ALS) mettent en œuvre des structures dans lesquelles le couplage des entrées n'est plus réalisé par un transistor mais par un montage à base de diodes Schottky. Néanmoins, comme ces séries découlent directement des premières séries TTL et en reproduisent les caractéristiques essentielles et une grande partie de la structure, les constructeurs ont continué de les qualifier de « TTL ». Toutefois, il apparaît que ce point de vue a été abandonné dans leurs documentations techniques les plus récentes.

Caractéristiques[modifier | modifier le code]

Alimentation[modifier | modifier le code]

La technologie TTL est normalisée pour une tension d'alimentation (VCC) de 5 V.

La tolérance sur la tension d'alimentation est de ±5 % (±0,25 V) pour les séries commerciales et industrielles (caractéristiques et fonctionnement garantis entre 0 °C et +70 °C), et de ±10 % (±0,5 V) pour les séries militaires (caractéristiques et fonctionnement garantis entre −55 °C et +125 °C).

La consommation de courant sur l'alimentation dépend de la complexité du circuit et de la série TTL à laquelle il appartient. Cette consommation varie avec la température, les états logiques et les courants circulant au travers des entrées et sorties. Elle augmente également avec la fréquence des transitions logiques quand cette fréquence devient élevée (toutes autres conditions étant fixées par ailleurs, la consommation moyenne reste pratiquement constante aux basses fréquences).

Exemples de consommation de courant :

| Circuit | ICCH | ICCL | Unité | ||

|---|---|---|---|---|---|

| typ. | max. | typ. | max. | ||

| SN7400 | 4 | 8 | 12 | 22 | mA |

| SN74LS00 | 0,8 | 1,6 | 2,4 | 4,4 | mA |

| SN74S00 | 10 | 16 | 20 | 36 | mA |

ICCH : courant d'alimentation, sorties à l'état haut

ICCL : courant d'alimentation, sorties à l'état bas

typ. : valeur typique ; max. : valeur maximale

Source : datasheet des circuits SN74x00 (4 portes NAND à deux entrées), Texas Instruments, 1983

Tensions et courants d'entrée et de sortie[modifier | modifier le code]

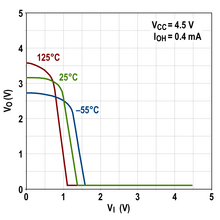

Un signal TTL est défini comme niveau logique bas entre 0 V et 0,8 V (VIL), et comme niveau logique haut entre 2,0 V et 5 V (VIH)[5]. Lorsqu'il est appliqué à l'entrée d'un circuit TTL, un signal conforme à ces plages de tension garantit la bonne interprétation des niveaux logiques correspondants. Ces niveaux varient légèrement entre les différentes séries et selon le constructeur (par exemple VIL est réduite à 0,7 V pour le SN54LS00 de Texas Instruments).

Par ailleurs, afin de garantir une relative immunité au bruit, les signaux logiques produits par la sortie d'un circuit TTL correspondent à des plages de tension spécifiées plus réduites : la tension de sortie minimale au niveau haut VOH est supérieure à VIH, et la tension de sortie maximale au niveau bas VOL est inférieure à VIL. Le circuit supporte un bruit d'autant plus important que les différences entre VOH et VIH d'une part (marge de bruit à l'état haut) et entre VIL et VOL d'autre part (marge de bruit à l'état bas) sont élevées.

Exemple de niveaux de tension, spécifiés pour les portes logiques TTL de Fairchild Semiconductor[4], avec les marges de bruit correspondantes :

| Limites, en V | |||||

|---|---|---|---|---|---|

| Séries TTL commerciales (0°C à +70°C) |

Entrée | Sortie | |||

| VIL | VIH | VOL | VOH | ||

| 74 | Standard TTL | 0,8 | 2,0 | 0,4 | 2,4 |

| 74H | High-speed TTL | 0,8 | 2,0 | 0,4 | 2,4 |

| 74L | Low-power TTL | 0,8 | 2,0 | 0,3 | 2,4 |

| 74S | Schottky TTL | 0,8 | 2,0 | 0,5 | 2,7 |

| 74LS | Low-power Schottky TTL | 0,8 | 2,0 | 0,5 | 2,7 |

| Marges de bruit, en V | |||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|

| au niveau BAS (VIL-VOL) | au niveau HAUT (VOH-VIH) | ||||||||||

| De : | Vers : | De : | Vers : | ||||||||

| 74 | 74H | 74L | 74S | 74LS | 74 | 74H | 74L | 74S | 74LS | ||

| 74 | 0,4 | 0,4 | 0,4 | 0,4 | 0,4 | 74 | 0,4 | 0,4 | 0,4 | 0,4 | 0,4 |

| 74H | 0,4 | 0,4 | 0,4 | 0,4 | 0,4 | 74H | 0,4 | 0,4 | 0,4 | 0,4 | 0,4 |

| 74L | 0,5 | 0,5 | 0,5 | 0,5 | 0,5 | 74L | 0,4 | 0,4 | 0,4 | 0,4 | 0,4 |

| 74S | 0,3 | 0,3 | 0,3 | 0,3 | 0,3 | 74S | 0,7 | 0,7 | 0,7 | 0,7 | 0,7 |

| 74LS | 0,3 | 0,3 | 0,3 | 0,3 | 0,3 | 74LS | 0,7 | 0,7 | 0,7 | 0,7 | 0,7 |

| Limites, en V | |||||

|---|---|---|---|---|---|

| Séries TTL militaires (-55°C à +125°C) |

Entrée | Sortie | |||

| VIL | VIH | VOL | VOH | ||

| 54 | Standard TTL | 0,8 | 2,0 | 0,4 | 2,4 |

| 54H | High-speed TTL | 0,8 | 2,0 | 0,4 | 2,4 |

| 54L | Low-power TTL | 0,7 | 2,0 | 0,3 | 2,4 |

| 54S | Schottky TTL | 0,8 | 2,0 | 0,5 | 2,5 |

| 54LS | Low-power Schottky TTL | 0,7 | 2,0 | 0,4 | 2,5 |

| Marges de bruit, en V | |||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|

| au niveau BAS (VIL-VOL) | au niveau HAUT (VOH-VIH) | ||||||||||

| De : | Vers : | De : | Vers : | ||||||||

| 54 | 54H | 54L | 54S | 54LS | 54 | 54H | 54L | 54S | 54LS | ||

| 54 | 0,4 | 0,4 | 0,3 | 0,4 | 0,4 | 54 | 0,4 | 0,4 | 0,4 | 0,4 | 0,4 |

| 54H | 0,4 | 0,4 | 0,3 | 0,4 | 0,4 | 54H | 0,4 | 0,4 | 0,4 | 0,4 | 0,4 |

| 54L | 0,5 | 0,5 | 0,4 | 0,5 | 0,5 | 54L | 0,4 | 0,4 | 0,4 | 0,4 | 0,4 |

| 54S | 0,3 | 0,3 | 0,2 | 0,3 | 0,3 | 54S | 0,5 | 0,5 | 0,5 | 0,5 | 0,5 |

| 54LS | 0,4 | 0,4 | 0,3 | 0,4 | 0,3 | 54LS | 0,5 | 0,5 | 0,5 | 0,5 | 0,5 |

Les conditions dans lesquelles ces niveaux de sortie sont définis varient selon la série TTL et l'état logique considérés, et peuvent varier légèrement d'un constructeur à l'autre. Les spécifications précisent notamment :

- IOL, la valeur maximale du courant produit par la sortie à la limite de tension spécifiée VOL (état bas)

- IOH, la valeur maximale (en valeur absolue) du courant produit par la sortie à la limite de tension spécifiée VOH (état haut)

- IIL, la valeur maximale (en valeur absolue) du courant résultant de l'application sur l'entrée d'un niveau logique bas

- IIH, la valeur maximale du courant résultant de l'application sur l'entrée d'un niveau logique haut.

NB : par convention, les courants sont négatifs quand ils sortent du composant.

L'entrée d'une porte TTL émet un courant notable à l'état bas (IIL) et absorbe un courant très faible à l'état haut (IIH), de quelques dizaines de µA au maximum. Par ailleurs, la capacité parasite de l'entrée doit être chargée ou déchargée par un courant durant les transitions. Ainsi, pour garantir le respect des niveaux logiques et pour limiter la durée des transitions, une sortie TTL connectée à une ou plusieurs entrées TTL doit pouvoir drainer un courant notable vers la masse à l'état bas et produire un courant beaucoup plus faible (mais néanmoins significatif) à l'état haut.

Il en résulte que les niveaux de tension de sortie des circuits TTL sont généralement définis pour des courants maximums nettement plus importants à l'état bas (IOL) qu'à l'état haut (IOH).

Il existe néanmoins des exceptions, comme celle des tampons TTL (buffers, en anglais) et pilotes de ligne de transmission (line drivers, en anglais), qui sont capables de fournir un courant important à l'état haut. À titre de comparaison :

| Circuit TTL | Fonction | Limites spécifiées | |

|---|---|---|---|

| IOH @ VOH | IOL @ VOL | ||

| DM74LS04 | 6 portes inverseuses (opérateur NON), avec entrées à hystérésis |

−0,4 mA @ 2,7 V | 4 mA @ 0,4 V 8 mA @ 0,5 V |

| DM74LS240 | 2 × 4 tampons inverseurs, avec entrées à hystérésis et sorties à trois états |

−1 mA @ 2,7 V −3 mA @ 2,4 V −15 mA @ 2,0 V |

12 mA @ 0,4 V 24 mA @ 0,5 V |

H = sortie au niveau haut (1 logique)

L = sortie au niveau bas (0 logique)

Exemple de niveaux de tension et de courant spécifiés pour les portes logiques de Texas Instruments[8] :

| Séries TTL |

Courants en mA | Tensions en V | ||||||

|---|---|---|---|---|---|---|---|---|

| Sortie | Entrée | Sortie | Entrée | |||||

| IOH | IOL | IIH | IIL | VOH | VOL | VIH | VIL | |

| 54/74 | -0,4 | 16 | 0,04 | -1,6 | 2,4 | 0,4 | 2,0 | 0,8 |

| 54H/74H | -0,5 | 20 | 0,05 | -2 | 2,4 | 0,4 | 2,0 | 0,8 |

| 54L | -0,1 | 2 | 0,01 | -0,18 | 2,4 | 0,3 | 2,0 | 0,7 |

| 74L | -0,2 | 3,6 | 0,01 | -0,18 | 2,4 | 0,4 | 2,0 | 0,7 |

| 54LS | -0,4 | 4 | 0,02 | -0,4 | 2,5 | 0,4 | 2,0 | 0,7 |

| 74LS | -0,4 | 8 | 0,02 | -0,4 | 2,7 | 0,5 | 2,0 | 0,8 |

| 54S | -1 | 20 | 0,05 | -2 | 2,5 | 0,5 | 2,0 | 0,8 |

| 74S | -1 | 20 | 0,05 | -2 | 2,7 | 0,5 | 2,0 | 0,8 |

| 54AS/74AS | -2 | 20 | 0,02 | -0,5 | 2,5 | 0,5 | 2,0 | 0,8 |

| 54ALS | -0,4 | 4 | 0,02 | -0,1 | 2,5 | 0,4 | 2,0 | 0,8 |

| 74ALS | -0,4 | 8 | 0,02 | -0,1 | 2,5 | 0,4 | 2,0 | 0,8 |

Ces limites de tensions et de courants permettent de définir la sortance (ou fan-out, en anglais), qui est le nombre maximum d'entrées de portes logiques auxquelles la sortie d'une porte logique peut être connectée.

Le tableau suivant, qui concerne les portes logiques TTL de Texas Instruments[8], distingue la sortance au niveau haut de la sortance au niveau bas afin de pouvoir considérer l'interconnexion de portes appartenant à des séries TTL différentes :

| Sortances par niveau logique, en fonction des séries TTL | ||||||||

|---|---|---|---|---|---|---|---|---|

| De : | Niveau logique |

Vers : | ||||||

| 54 74 |

54H 74H |

54L 74L |

54LS 74LS |

54S 74S |

54AS 74AS |

54ALS 74ALS | ||

| 54 74 |

H | 10 | 8 | 40 | 20 | 8 | 20 | 20 |

| L | 10 | 8 | 88,89 | 40 | 8 | 32 | 160 | |

| 54H 74H |

H | 12,5 | 10 | 50 | 25 | 10 | 25 | 25 |

| L | 12,5 | 10 | 111,11 | 50 | 10 | 40 | 200 | |

| 54L | H | 2,5 | 2 | 10 | 5 | 2 | 5 | 5 |

| L | 1,25 | 1 | 11,11 | 5 | 1 | 4 | 20 | |

| 74L | H | 5 | 4 | 20 | 10 | 4 | 10 | 10 |

| L | 2,25 | 1,8 | 20 | 9 | 1,8 | 7,2 | 36 | |

| 54LS | H | 10 | 8 | 40 | 20 | 8 | 20 | 20 |

| L | 2,5 | 2 | 22,22 | 10 | 2 | 8 | 40 | |

| 74LS | H | 10 | 8 | 40 | 20 | 8 | 20 | 20 |

| L | 5 | 4 | 44,44 | 20 | 4 | 16 | 80 | |

| 54S 74S |

H | 25 | 20 | 100 | 50 | 20 | 50 | 50 |

| L | 12,5 | 10 | 111,11 | 50 | 10 | 40 | 200 | |

| 54AS 74AS |

H | 50 | 40 | 200 | 100 | 40 | 100 | 100 |

| L | 12,5 | 10 | 111,11 | 50 | 10 | 40 | 200 | |

| 54ALS | H | 10 | 8 | 40 | 20 | 8 | 20 | 20 |

| L | 2,5 | 2 | 22,22 | 10 | 2 | 8 | 40 | |

| 74ALS | H | 10 | 8 | 40 | 20 | 8 | 20 | 20 |

| L | 5 | 4 | 44,44 | 20 | 4 | 16 | 80 | |

H : niveau haut ; L : niveau bas

Les cases grisées du tableau mettent en correspondance des entrées et sorties de portes logiques appartenant à la même série TTL.

Considérant la sortie d'une porte logique, chaque entrée qui y est connectée consomme une fraction de sa sortance. Pour qu'un montage soit correct, il est nécessaire que la somme de ces fractions ne dépasse pas la sortance disponible, ni au niveau haut, ni au niveau bas.

Par exemple, d'après le tableau précédent, la sortie d'une porte 74L peut être connectée simultanément à l'entrée d'une porte 74H et de trois portes 74AS, car :

- au niveau haut (H) : 1 − 14 − 310 ≥ 0

- au niveau bas (L) : 1 − 11,8 − 37,2 ≥ 0

A contrario, il n'est pas possible de connecter l'entrée de six portes 74H à la sortie d'une porte 74LS, car si l'on a bien 1 − 68 ≥ 0 au niveau haut, on a 1 − 64 < 0 au niveau bas.

Remarque : la sortance n'est pas définie relativement au nombre d'entrées physiques de circuits logiques, mais relativement à un nombre équivalent d'entrées de portes logiques classiques, du point de vue des caractéristiques électriques garanties. Ainsi, on doit notamment tenir compte du fait qu'un tampon peut présenter une sortance supérieure à celle d'une porte logique classique, ou encore que l'entrée d'un circuit logique complexe peut être connectée à plusieurs entrées de ses portes logiques internes.

Comportement dynamique[modifier | modifier le code]

Les systèmes numériques électroniques sont caractérisés par différents délais dans la propagation des signaux à travers les circuits logiques et à travers leurs interconnexions. Ces délais limitent leur vitesse de fonctionnement et sont susceptibles d'affecter le comportement des circuits de logique séquentielle.

Néanmoins, ces délais confèrent aux circuits une relative immunité aux courtes impulsions parasites.

On constate que les portes TTL Schottky (série 74S) sont plus rapides que les portes TTL standard (série 7400), mais qu'elles sont sensibles à des impulsions parasites plus courtes et de plus faible amplitude.

Les délais de propagation des signaux à l'intérieur d'un même circuit intégré dépendent de sa complexité et de la série TTL utilisée. Ils peuvent varier selon le sens des transitions (montant ou descendant) et selon les conditions d'utilisation (température, tension d'alimentation, charge extérieure).

On les définit comme suit :

- tPHL = temps de propagation d'un signal logique produisant une transition haut→bas sur la sortie

- tPLH = temps de propagation d'un signal logique produisant une transition bas→haut sur la sortie

Exemples de temps de propagation spécifiés pour les portes NON-ET ('00) de différentes séries TTL :

- d'après Fairchild[4]

| Série TTL | 54/7400 | 54/74H00 | 54/74S00 | 54/74LS00 | Unité | ||||

|---|---|---|---|---|---|---|---|---|---|

| Valeurs | Min | Max | Min | Max | Min | Max | Min | Max | |

| tPHL | – | 15 | – | 10 | 2.0 | 4.5 | – | 10 | ns |

| tPLH | – | 22 | – | 10 | 2.0 | 4.5 | – | 10 | ns |

| Conditions | CL=15 pF RL=400 Ω |

CL=15 pF RL=280 Ω |

CL=15 pF RL=280 Ω |

CL=15 pF – |

|||||

- d'après Texas Instruments[9]

| Porte TTL | SN54/7400 | SN54/74S00 | SN54/74LS00 | Unité | |||

|---|---|---|---|---|---|---|---|

| Valeurs | typ. | max. | typ. | max. | typ. | max. | |

| tPHL | 7 | 15 | 3 | 5 | 10 | 15 | ns |

| tPLH | 11 | 22 | 3 | 4.5 | 9 | 15 | ns |

| Conditions | CL=15 pF RL=400 Ω |

CL=15 pF RL=280 Ω |

CL=15 pF RL=2 kΩ |

||||

Valeurs mesurées à TA = 25 °C (température ambiante) et VCC = 5 V

CL, RL : charge de test connectée à la sortie de la porte

min. : valeur minimale ; typ. valeur typique ; max. : valeur maximale

Les temps de transition du signal à la sortie d'une porte logique intervenant dans les délais de propagation, ces derniers augmentent lorsque la charge connectée à la sortie est plus importante :

Les délais d'établissement des niveaux logiques transmis entre une sortie TTL et les entrées qui y sont connectées dépendent de la mise en œuvre des circuits intégrés (géométrie des conducteurs électriques, nature des isolants) et des caractéristiques électriques de cette sortie (sortance) et de ces entrées (entrance).

Pour les interconnexions réalisées sur des distances assez faibles, les conducteurs de liaison sont assimilables à des capacités parasites et les signaux ne subissent pas de dégradations notables propres aux lignes de transmission (réflexions et suroscillations notamment – ces dégradations sont favorisées par le caractère variable des impédances d'entrée et de sortie des circuits TTL, lesquelles ne peuvent donc correspondre en permanence à l'impédance caractéristique fixe de la ligne de transmission). Les temps de transition des signaux transmis dépendent, d'une part, de la somme de ces capacités parasites et de celles des entrées TTL et, d'autre part, des courants que la sortie TTL est capable de produire pour charger et décharger l'ensemble de ces capacités. Les transitions sont d'autant plus courtes que les capacités sont faibles et que les courants sont élevés.

Exemple de longueurs maximales d'interconnexion sans effet notable propre aux lignes de transmission, pour différentes séries TTL (d'après Fairchild[4]) :

| Série TTL | Temps de montée |

Temps de descente |

Longueur maximale |

|---|---|---|---|

| 54/74 | 6 à 9 ns | 4 à 6 ns | 45 cm |

| 54/74H, 54/74LS |

4 à 6 ns | 2 à 3 ns | 22,5 cm |

| 54/74S | 1,8 à 2,8 ns | 1,6 à 2,6 ns | 19 cm |

(Valeurs relevées pour une vitesse de propagation de 5,6 ns/m, sur circuit imprimé en verre epoxy de constante diélectrique εr = 4,7)

Mis à part quelques références spécifiques (p. ex. les tampons 74S140) et les séries les plus récentes (AS et ALS notamment), les circuits logiques TTL n'ont pas été conçus pour être interconnectés au travers de lignes de transmission, en dépit des dispositifs internes ajoutés pour contrecarrer certains de leurs effets (p. ex. les diodes de clampage présentes sur les entrées pour absorber les suroscillations). Ils réclament donc des efforts de conception particuliers quand la longueur des interconnexions devient trop importante.

Compatibilité TTL[modifier | modifier le code]

Quand une famille de circuits logiques basée sur une technologie différente de la technologie TTL présente des caractéristiques conformes aux limites spécifiées communes aux circuits TTL (tensions et courants), on la qualifie de « compatible TTL ». Ces circuits sont conçus pour remplacer les circuits en technologie TTL tout en améliorant les performances (immunité au bruit, consommation électrique, vitesse, etc.) ou pour y être directement interconnectés. Dans leur cas, on peut encore parler de signaux TTL et de niveaux logiques TTL, mais plus de circuits TTL.

Les familles de circuits HCMOS compatibles TTL (HCT), Advanced CMOS compatibles TTL (ACT), Advanced BiCMOS Technology (ABT), Low Voltage Technology (LVT) et Advanced LVT (ALVT) en sont des exemples.

Les circuits des familles LVT et ALVT, réalisés en technique BiCMOS, sont qualifiés de compatibles LVTTL (Low Voltage TTL, ou « TTL basse tension » en français) du fait de leur tension d'alimentation réduite à 3,3 V (au lieu de 5 V pour la famille TTL) et de la compatibilité TTL de leurs niveaux logiques. Néanmoins, certains de ces circuits ayant la capacité de fonctionner sous des tensions d'alimentation encore plus faibles (p. ex. 2,5 V[10]), ils perdent leur compatibilité TTL lorsqu'ils sont utilisés dans ces conditions.

Toutefois, lorsque les circonstances particulières le permettent, il est possible qu'un circuit logique dont les caractéristiques ne sont pas totalement conformes aux spécifications des circuits TTL puisse tout de même y être directement interconnecté. Par exemple, moyennant une réduction des tolérances, on peut interconnecter directement une porte TTL et une porte 74LVC alimentée en 2,5 V, et la sortie d'une porte 74HC alimentée en 5 V peut piloter directement l'entrée d'une porte TTL (l'inverse n'est pas permis).

Avantages[modifier | modifier le code]

- Cette famille de composants allie une bonne vitesse de commutation à un faible temps de transfert.

- L'immunité aux parasites est bonne à condition de découpler l'alimentation au plus près de chaque circuit par un condensateur de filtrage.

- Par défaut, une entrée en l'air (sans niveau de tension fixé extérieurement) est à l'état logique « 1 » (elle ne débite un courant notable que lorsqu'on la force à l'état logique « 0 », où elle se comporte de façon équivalente à une résistance de rappel à VCC=5 V). Néanmoins, les constructeurs préconisent de toujours connecter une entrée restant à l'état logique « 1 » à un potentiel fixe supérieur à 2,5 V, afin notamment de ne pas dégrader les performances dynamiques des autres entrées de la porte logique TTL.

Inconvénients[modifier | modifier le code]

- L'alimentation des circuits TTL doit être précise : +5 V ±5 %, en comparaison aux circuits CMOS qui ont, eux, une plage de tension d'alimentation bien plus vaste (de +3 à +18 V). En cas de non-respect de cet impératif, on risque, au mieux, un fonctionnement erratique du circuit, et au pire, une destruction partielle ou complète du circuit.

- La technique bipolaire est grande consommatrice de courant électrique ; les mémoires en TTL sont certes rapides, mais ne peuvent guère être sauvegardées bien longtemps en cas de coupure d'alimentation.

- On ne peut transmettre les signaux émis par les circuits TTL sans circuits de transmission additionnels sur de grandes distances sans pertes : longueur maximum environ 15 m.

La famille TTL[modifier | modifier le code]

Durant les années qui ont suivi l'invention de la technologie TTL, les différents constructeurs de circuits intégrés ont proposé des composants TTL relativement disparates en termes de configuration et de désignation. Initiée par Texas Instruments, la série de circuits 5400 et sa déclinaison 7400 (pour les applications commerciales et industrielles courantes, par opposition aux applications spatiales et militaires plus exigeantes) s'est ensuite imposée comme une référence commune.

Depuis lors, la désignation d'un circuit de la famille TTL est généralement composée du nombre 74 ou 54, suivi éventuellement d'une ou plusieurs lettres correspondant à la série liée à une évolution majeure de la technologie TTL (absence de lettre pour la série standard) puis d'un nombre de deux à quatre chiffres correspondant à la fonction logique réalisée par le circuit. Elle peut contenir un préfixe spécifique au constructeur (p. ex. SN pour Texas Instruments) et un suffixe qui apporte des informations complémentaires telles que le type de boîtier (p. ex. N pour les boîtiers DIP en plastique) ou une variante dans les spécifications.

Les principales séries appartenant à la famille TTL sont :

- TTL[11],[12] : série standard

- TTL-L[11] (Low power) : série à faible consommation

- TTL-H[4] (High-speed) : série rapide

- TTL-S[11],[12] (Schottky) : série rapide à transistors Schottky

- TTL-LS[11],[12] (Low power Schottky) : combinaison des technologies L et S, c'est la famille la plus répandue

- TTL-F[13] (FAST : Fairchild Advanced Schottky Technology)

- TTL-AS[14] (Advanced Schottky) : version améliorée de la série S

- TTL-ALS[15] (Advanced Low power Schottky) : version améliorée de la série LS

Évolutions[modifier | modifier le code]

Afin de combiner les avantages des techniques bipolaire (vitesse) et CMOS (faible consommation, large plage de tension) les ingénieurs se sont attachés à concevoir d'autres types de circuit logique reprenant les fonctions des séries TTL classiques. Dans l'ordre chronologique :

- HCMOS 74HCxx (incompatible avec les niveaux logiques TTL, VCC = 2 V à 6 V, temps de propagation minimal = 20 ns pour VCC = 6 V, au-delà de 100 ns pour VCC = 2 V).

- HCMOS compatible TTL 74HCTxx (VCC = 4,5 V à 5,5 V, temps de propagation typique = 20 ns).

- Advanced BiCMOS 74ABTxx (compatible TTL, combine les technologies CMOS et bipolaire pour une faible consommation et des courants de sortie élevés, temps de propagation typique = 3 ns)

- Advanced HCMOS 74AHCxx (incompatible avec les niveaux logiques TTL, plus rapide que 74HCxx, temps de propagation typique = 5 ns)

- Advanced HCMOS compatible TTL 74AHCTxx (plus rapide que 74HCTxx, temps de propagation typique = 5 ns)

- Low-Voltage BiCMOS Technology 74LVTxx (compatible TTL avec une tension d'alimentation de 3,3V, combine les technologies CMOS et bipolaire, temps de propagation typique = 2 ns)

- Advanced Low-Voltage BiCMOS Technology 74ALVTxx (plus rapide que 74LVTxx, temps de propagation typique = 1,5 ns)

Exemples[modifier | modifier le code]

Circuit 7400[modifier | modifier le code]

Le circuit 7400 est un quadruple « NON-ET » (NAND).

On alimente le circuit de la manière suivante : VCC sur la broche 14 (+5 V) et la masse sur la broche 7.

On peut utiliser chacune des quatre portes de la manière suivante :

- porte NAND-1, entrées A et B sur les broches 1 et 2, sortie sur la broche 3.

- porte NAND-2, entrées A et B sur les broches 4 et 5, sortie sur la broche 6.

- porte NAND-3, entrées A et B sur les broches 9 et 10, sortie sur la broche 8.

- porte NAND-4, entrées A et B sur les broches 12 et 13, sortie sur la broche 11.

Bien sûr les portes sont indépendantes les unes des autres, si certaines des portes ne sont pas utilisées, on peut relier leurs entrées A et B au +VCC (ou à la masse) et laisser la sortie « en l'air ».

Note : les entrées A et B sont interchangeables l'une avec l'autre.

Compteur 7490[modifier | modifier le code]

Le compteur 7490 est un compteur asynchrone décimal (composé de 4 bascules JK).

Notes et références[modifier | modifier le code]

- (en) Brevet US3283170A déposé le 8 septembre 1961 par James L. Buie

- (en) New forms of all-transistor logic par R. Beeson et H. Ruegg - 1962 IEEE International Solid-State Circuits Conference. Digest of Technical Papers. DOI: 10.1109/ISSCC.1962.1157368

- (en) The TTL Data Book Vol. 2 Texas Instruments 1985

- (en) TTL Data Book Fairchild 1978

- (en) Logic voltage levels

- (en) DC Electrical Characteristics of MM74HC high-Speed CMOS Logic, Fairchild 1998 (page 2, comparaison avec LS00)

- (en) Input and Output Characteristics of Digital Integrated Circuits, Texas Instruments, 1996

- (en) Texas Instruments Advanced Schottky Family, 1985

- (en) SNx400, SNx4LS00, and SNx4S00 Quadruple 2-Input Positive-NAND Gates, Texas Instruments, 1983 rev. 2017

- (en) 74ALVT16952 2.5V/3.3V ALVT 16-bit registered transceiver (3-State), Philips Semiconductors, 1998

- (en) LS/S/TTL Logic Databook National Semiconductor 1989

- (en) TTL Logic - Standard TTL, Schottky, Low-Power Schottky Data Book Texas Instruments 1988

- (en) FAST - Fairchild Advanced Schottky TTL Fairchild 1981

- (en) Advanced Schottky Databook National Semiconductor 1982

- (en) LSI Logic Data Book Texas Instruments 1986

Voir aussi[modifier | modifier le code]

Articles connexes[modifier | modifier le code]

- Fonction logique

- Tableau de Karnaugh

- Électronique numérique

- Additionneur

- Multiplexeur

- VHDL

- CMOS

- Liste des circuits intégrés de la série 7400

Liens externes[modifier | modifier le code]

- Circuits intégrés logiques TTL

- Technologie des fonctions logiques TTL et CMOS

- Circuits TTL 74xx, contient une liste de circuits TTL